Sic Mosfet Gate Driver Design

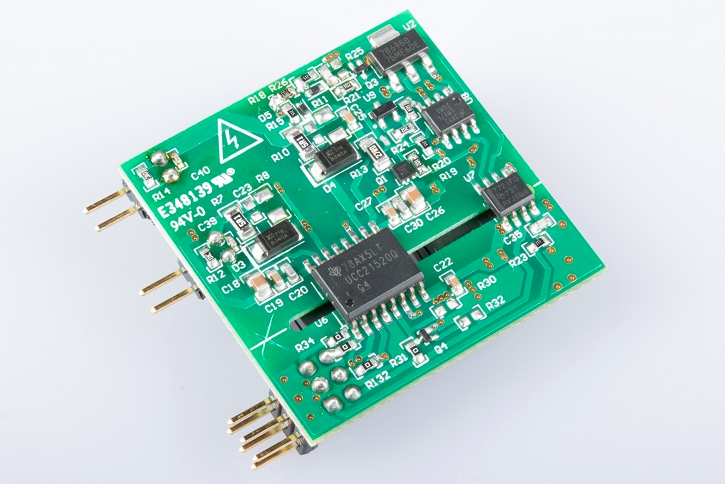

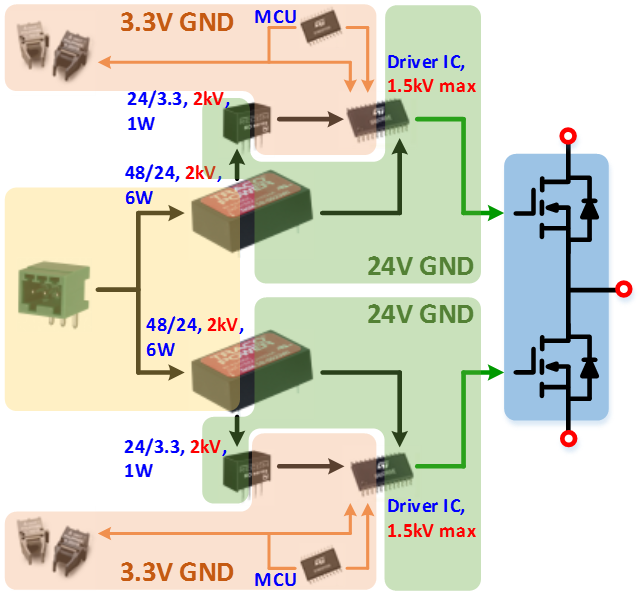

Gate driver pcb layout.

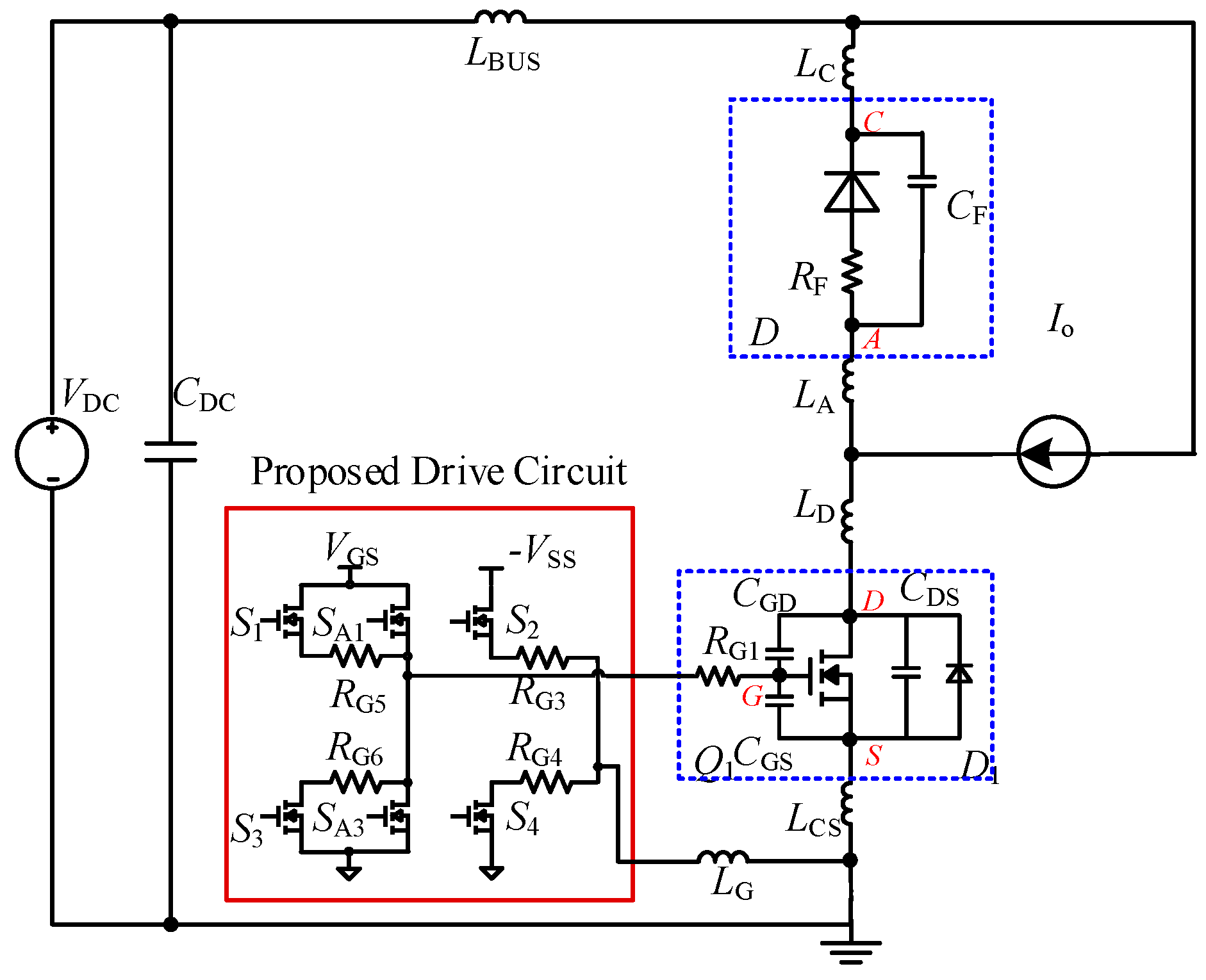

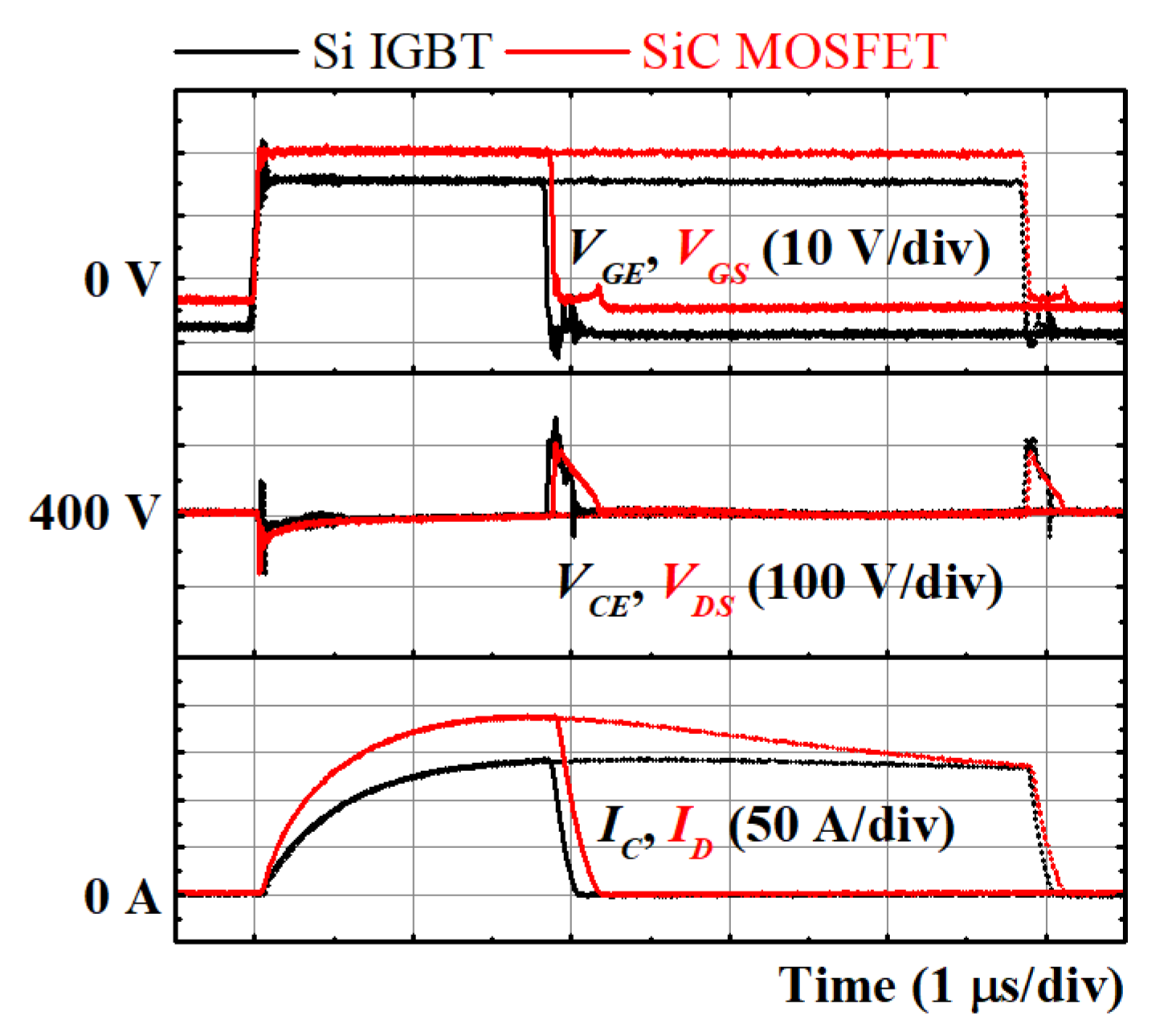

Sic mosfet gate driver design. Mscsicmdd ref1 dual sic mosfet driver reference design an1824 application note revision 1 1 3 the sic mosfets are normally driven at higher asymmetrical gate voltages when compared to silicon mosfets. Typically they are driven at 5 v to 20 v. Wolfspeed s cgd15sg00d2 is a gate driver board specifically designed to support 900v and 1200v 3rd generation sic mosfets with high creepage 9mm clearance. There are new commercially available sic mosfets available in discrete and module packages which are much faster and more efficient than their traditional igbt counterparts.

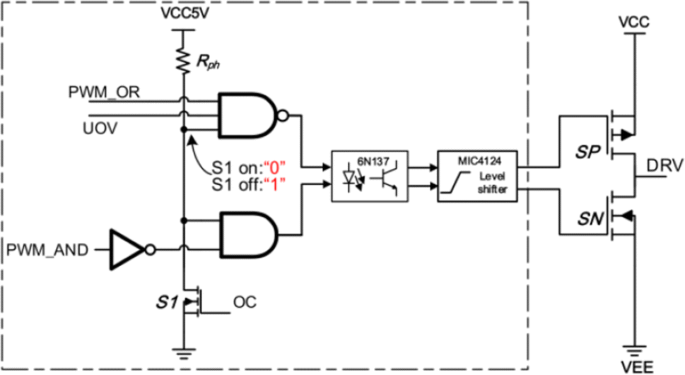

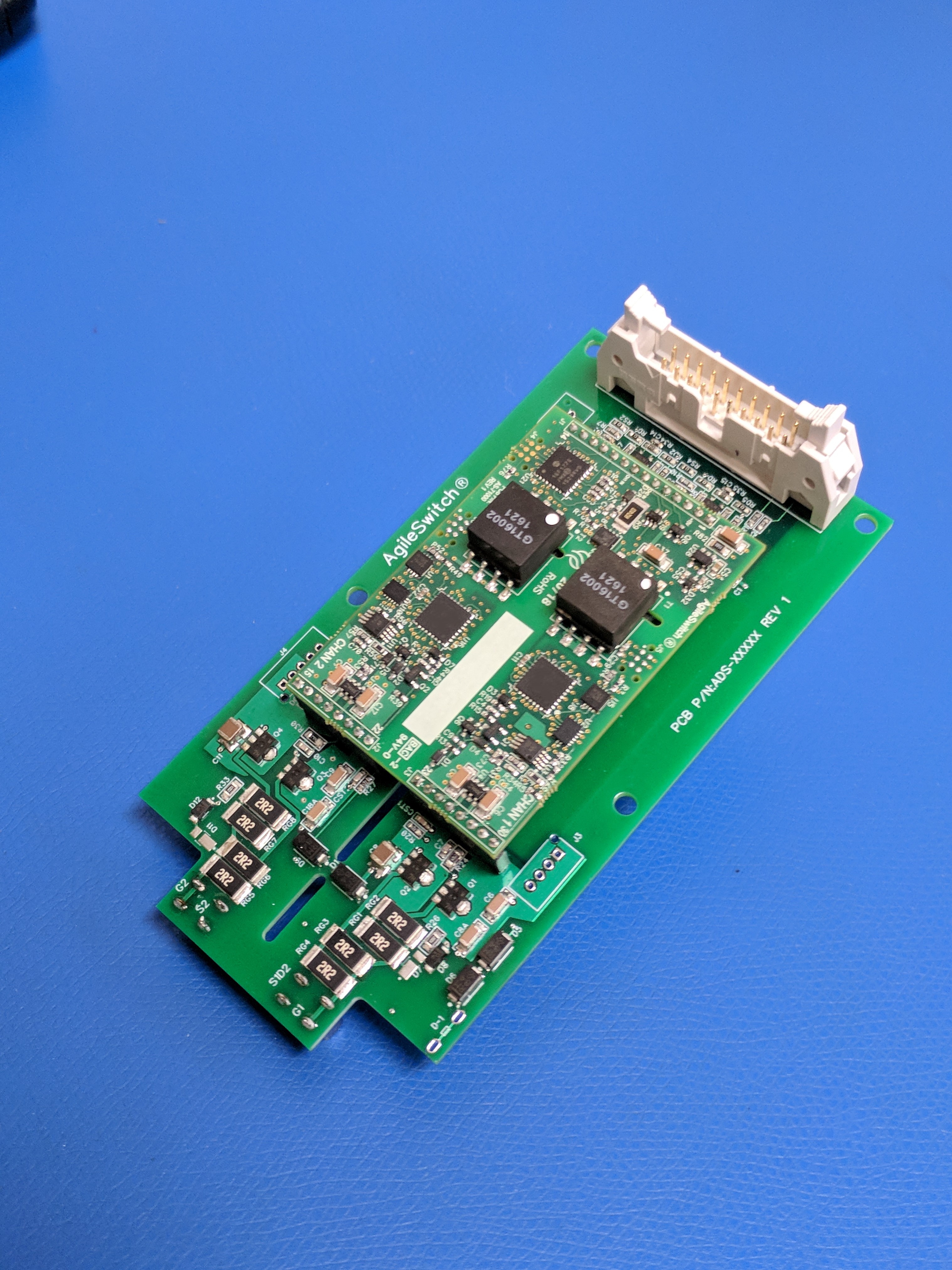

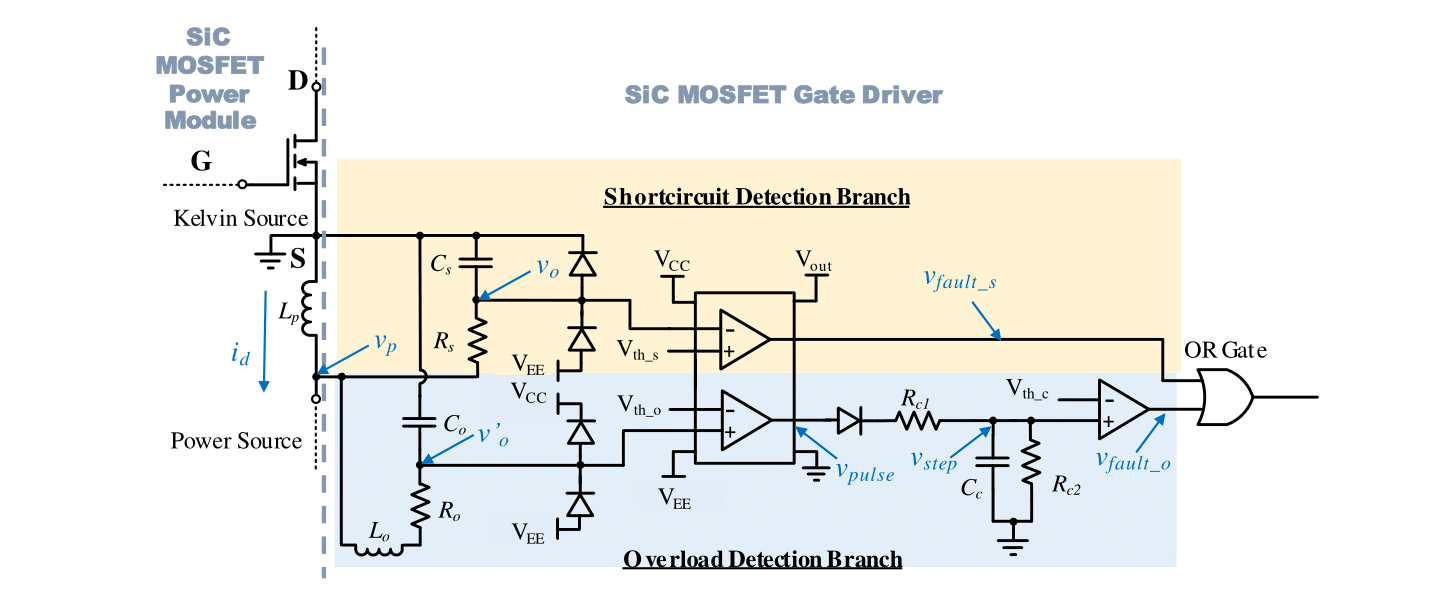

The purpose of this paper is to provide guidance on how to design gate driver circuits for silicon carbide sic mosfets. The 6 mω module has dual gate source pins and dual power drain and source connection points to reduce inductance and improve current sharing amongst the sic mosfet chips internal to the module. Microchip s agileswitch digitally programmable gate driver and sp6li sic power module kit provide design engineers with a central point of contact for. This includes modes optimized for half bridge switching with synchronous dead time protection and asynchronous signal transfer with no protection.

What is a power mosfet gate driver. In an application note about fine tuning sic mosfet gate drivers stmicroelectronics recommends making rgon at least 1 5 times rgoff with resistance values of about 4 7ω and 2 2ω respectively. Lower positive voltages can be used if the resulting higher r is acceptable. While this e book goes into further detail you can jump into the most relevant topics for your design at the right.

Sic mosfet gate drive design considerations abstract. Igbt sic gate driver fundamentals. Gate driver circuit. Discover solutions to some of the most commonly asked igbt and sic gate driver questions.

The reference design provides customers with a highly isolated sic mosfet dual gate driver switch to provide a means for evaluating sic mosfets in a number of topologies. There are also other desirable driver features to consider including close delay matching fast desaturation protection under voltage lockout.